# LibrePCB Documentation

2024-12-01

# **Table of Contents**

| Installation                 | 2 |

|------------------------------|---|

| Official Binaries            | 2 |

| Distribution Packages        | 2 |

| Build From Sources           | 2 |

| On Windows                   | 2 |

| Installer                    | 3 |

| Portable Package             | 3 |

| On Linux.                    | 3 |

| Portable AppImage (x86_64)   | 3 |

| Snap Package (multi-arch)    | 4 |

| Flatpak (multi-arch)         | 4 |

| Online Installer (abandoned) | 5 |

| On macOS                     | 5 |

| Portable Package             | 5 |

| Online Installer (abandoned) | 5 |

| Build From Sources           | 5 |

| Requirements                 | 5 |

| Get the Sources              | 6 |

| Build LibrePCB               | 6 |

| Additional Resources         | 6 |

| Quickstart Tutorial          | 7 |

| Create a Workspace           | 7 |

| Install Remote Libraries     | 9 |

| Create a Local Library       | 1 |

| Create a PCB Project         | 3 |

| Create Schematics            | 6 |

| Create Board                 | 9 |

| Order PCB                    | 8 |

| Create Library Elements      | 2 |

| Concept Overview             | 3 |

| Our Example: LMV321LILT      | 4 |

| Component Category           | 5 |

| Symbol                       | 6 |

| Component                    | 1 |

| Package Category             | 6 |

| Package                      | 7 |

| Device                       | 3 |

| User Manual                  | 5 |

| Layers                 | 5 |

|------------------------|---|

| Schematic Layers       | 5 |

| Board Layers           | 3 |

| Custom Layers          | ) |

| Licenses               | ) |

| Available Licenses     | ) |

| Other Licenses         | ) |

| Additional Actions     | L |

| Recommendation         | L |

| License of Libraries   | L |

| Project Editor         | L |

| Assembly Data          | L |

| Output Jobs            | ) |

| Command-Line Interface | 7 |

| Installation           | 7 |

| Binary Releases        | 7 |

| Docker Image           | 3 |

| Show Help Text         | 3 |

| Command "open-library" | 3 |

| Examples               | ) |

| Command "open-project" | ) |

| Examples               | 2 |

| Library Conventions    | ł |

| Symbol Conventions     | ł |

| Generic vs. Specific   | ł |

| Naming                 | ł |

| Origin                 | 5 |

| Outline                | 5 |

| Pin Placement          | 3 |

| Pin Naming             | 3 |

| Text Elements          | ; |

| Grab Area              | 7 |

| Package Conventions    | 7 |

| Scope                  | 7 |

| Naming                 | 3 |

| Pads                   | 3 |

| Footprints             | ) |

| Origin                 | ) |

| Orientation            |   |

| Legend Layer           |   |

| Documentation Layer    | 2 |

| Package Outlines Layer                |

|---------------------------------------|

| Courtyard Layer                       |

| Text Elements                         |

| 3D Models                             |

| ۲roubleshooting                       |

| Workspace Sync (Dropbox, Cloud, Git,) |

| Wayland                               |

| Slow/Laggy UI                         |

| Logging Output                        |

| Reporting Problems                    |

| Development                           |

### Welcome to the documentation of LibrePCB 1.2.0!

The documentation is still work in progress. Help us writing beautiful documentation on GitHub!

#### Video Tutorials

In addition to this documentation in written form, there are also video tutorials available on our YouTube channel.

#### Offline Documentation

For offline- or printable documentation, use the PDF download link at the bottom left of the page.

Chapters:

- Installation

- Quickstart Tutorial

- User Manual

- CLI Reference

- Library Conventions

- Troubleshooting

- Development

Didn't find what you're looking for? Contact us!

# Installation

## **Official Binaries**

We provide official binary releases for the following operating systems:

- Windows

- Linux

- macOS

## **Distribution Packages**

In addition, we are officially maintaining the following packages:

- Snap on Snapcraft

- Flatpak on Flathub

For other systems, a LibrePCB package might be provided by a package maintainer, either partially related or unrelated to the LibrePCB developers. We are aware of the following packages:

- Chocolatey Package (Windows)

- Homebrew Cask Package (MacOS)

- Arch Linux AUR Package (builds from source)

- NixOS Package

- Gentoo Package

- OpenPandora Package

- Void Linux Package

As these packages are not under our control, we cannot guarantee their genuineness and correctness.

You're a LibrePCB package maintainer? Ask us to list your package here!

## **Build From Sources**

Since LibrePCB is a free & open-source application, you can compile it by yourself if you like. This allows to run LibrePCB even on systems where no pre-built binaries are available. See instructions at Build From Sources.

## **On Windows**

## Installer

The recommended way to install LibrePCB is to use the installer.

**Just download and run librepcb-installer-1.2.0-windows-x86\_64.exe.** Afterwards you'll find LibrePCB in your start menu.

0

Unfortunately we're not able yet to sign our Windows installer (it's quite expensive to do it). Therefore Windows might warn that the publisher of the installer is unknown. This is normal for binaries without paying for a signature, therefore just click on **[More info]** and then **[Run anyway]** to skip the warning.

For automated (unattended) installation, please check out the command-line parameters of the Inno Setup framework here (uninstall):

a

librepcb-installer-1.2.0-windows-x86\_64.exe /VERYSILENT

/SUPPRESSMSGBOXES

## **Portable Package**

Alternatively you could run LibrePCB without installing it. But then you don't get start menu entries and LibrePCB file extensions won't be registered so you can't open LibrePCB projects with a doubleclick in the file manager.

Download and extract librepcb-1.2.0-windows-x86\_64.zip, then run the contained file bin\librepcb.exe.

## On Linux

Due to the diversity of the Linux ecosystem, there are many different ways to install LibrePCB. The order of the options provided below do not reflect any recommendation.

If you're unsure, here our recommendations:

- )

- On Ubuntu: Snap Package

- On a Raspberry Pi: Flatpak

- Everywhere else: Portable AppImage

### Portable AppImage (x86\_64)

The AppImage is a single-file portable package which runs on most Linux distributions. It is fully functional without installing anything on your system, but it does not provide an update mechanism.

Download librepcb-1.2.0-linux-x86\_64.AppImage, make it executable and run it:

```

wget "https://download.librepcb.org/releases/1.2.0/librepcb-1.2.0-linux-

x86_64.AppImage"

chmod +x ./librepcb-1.2.0-linux-x86_64.AppImage

./librepcb-1.2.0-linux-x86_64.AppImage

```

If you're not familiar with the terminal: Right-click on the downloaded file and then check something like *Allow executing file as program* or *Run as executable*. Afterwards double-click the file to run it.

## Snap Package (multi-arch)

For distrubutions like Ubuntu which use the Snap package manager, probably the easiest way is to install the LibrePCB Snap package.

On Ubuntu, just open the *Ubuntu Software* application (app store), search for LibrePCB and install it. Alternatively, run this command from in the terminal:

sudo snap install librepcb

Some users reported that LibrePCB crashes when installed as a Snap package. It seems to be a problem related to fonts and Snap. If you experience this issue, the following workaround might help:

```

E

```

sudo rm /var/cache/fontconfig/\*

rm ~/.cache/fontconfig/\*

fc-cache -r

For more information about Snap, check out its documentation.

## Flatpak (multi-arch)

LibrePCB is also available as a Flatpak package from Flathub. Assuming you have followed the Flatpak setup steps, you can configure Flathub and install LibrePCB as follows:

After installing Flatpak itself, make sure to **reboot the computer** before executing the follwing commands! Otherwise LibrePCB might not appear in your application launcher.

flatpak remote-add --if-not-exists flathub

https://flathub.org/repo/flathub.flatpakrepo

flatpak install flathub org.librepcb.LibrePCB

## Online Installer (abandoned)

Note that starting with LibrePCB 1.0, we do no longer provide an installer for Linux. If you installed a previous LibrePCB release with the installer, please uninstall it with the *LibrePCB Maintenance Tool* and install the latest release with a different installation method instead.

## **On macOS**

### **Portable Package**

To install LibrePCB, download the portable \*.dmg file matching your CPU architecture:

- Intel (x86\_64): librepcb-1.2.0-mac-x86\_64.dmg

- Apple Silicon (arm64): librepcb-1.2.0-mac-arm64.dmg

Double-click the downloaded file in Finder. Then drag and drop the LibrePCB app onto the "Applications" folder in Finder. Afterwards you'll find LibrePCB in the Launchpad.

Unfortunately we're not able (yet) to officially sign the macOS binary. Therefore macOS refuses to start LibrePCB by default. As a workaround, you need to run it once with **Right-click > Open** on the LibrePCB application in the Launchpad. If this doesn't work, try it a second time.

Afterwards you should be able to run LibrePCB normally with a single click.

### **Online Installer (abandoned)**

Note that starting with LibrePCB 1.0, we do no longer provide an installer for macOS. If you installed a previous LibrePCB release with the installer, please uninstall it with the *LibrePCB Maintenance Tool* and install the latest release with the Portable Package instead.

## **Build From Sources**

### Requirements

To compile LibrePCB, you need to install the following tools & libraries first:

- g++ >= 4.8, MinGW >= 4.8, or Clang >= 3.3 (C++11 support is required)

- Qt >= 5.5

- OpenCASCADE OCCT or OCE (optional)

- OpenGL Utility Library GLU (optional)

- zlib

- OpenSSL

- CMake 3.5 or newer

### **Get the Sources**

It is very important to use the correct sources:

- Do NOT clone any branch (e.g. master) from our repository on GitHub! These sources are not compatible with the stable file format of LibrePCB.

- Do NOT use the archives provided at the GitHub Releases page. These do not include the submodules and thus can't be compiled.

- It's fine to clone the official release **tag** (current: 1.2.0) from our repository on GitHub, just keep in mind to pass --recursive to also get all the submodules.

For convenience, we provide an official source archive which contains all the required files (including submodules) and has stripped any unnecessary files: librepcb-1.2.0-source.zip

```

wget "https://download.librepcb.org/releases/1.2.0/librepcb-1.2.0-source.zip"

unzip ./librepcb-1.2.0-source.zip

cd ./librepcb-1.2.0

```

### **Build LibrePCB**

Within the downloaded source directory, execute the following commands:

```

mkdir build && cd build

cmake ..

make -j8

```

### **Additional Resources**

These are just the most important commands. For more details (e.g. the available configuration flags), check out the following resources:

- **README.md** within the source archive

- Build instructions on our developers documentation

# **Quickstart Tutorial**

This chapter provides a quick introduction into LibrePCB, starting from workspace initialization and ending with how to order the designed PCB.

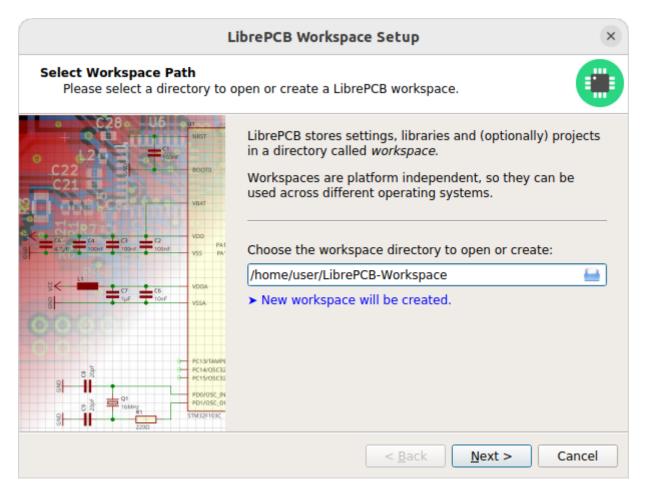

## **Create a Workspace**

When starting LibrePCB the first time, a wizard asks you to open or create a workspace. The workspace is just a directory where settings, libraries and (optionally) projects will be stored. Once created, it can be used from all supported operating systems (i.e. it is platform independent) and from any LibrePCB version.

You can just accept the default workspace location (you could still move it to another location afterwards, if desired):

If the selected path does not contain a workspace yet, clicking on **[Next]** will show a page to choose the most important settings:

| Set the most important work | space settings.                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                             | Language:<br>Preferred Norm:<br>Length Unit:<br>User Name: | System Language<br>IEC 60617<br>Millimeters<br>Me<br>This name will be used as authorised as authorised as authorised as authorised as authorised as authorised as a second |  |

It is recommended to select at least your **preferred norm** and **length unit** since these usually depend on where you're living.

You can change these settings at any time later in the control panel under **Extras > Workspace Settings**.

After clicking [ Finish ], the control panel shows up and you're ready to start using LibrePCB!

|                                                                           | Control Panel - Libre                                                        | РСВ                              | - • ×            |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------|------------------|

| <u>F</u> ile <u>E</u> xtras <u>H</u> elp                                  |                                                                              |                                  |                  |

| This workspace does not contain<br>You should <u>open the library man</u> | any libraries, which are essenti<br><mark>ager</mark> to add some libraries. | al to create and modify projects | Don't show again |

| Workspace Projects                                                        | New Project                                                                  | Open Project                     | Library Manager  |

|                                                                           | Recent Projects                                                              | Favorite Projects                |                  |

|                                                                           | Project description                                                          |                                  |                  |

|                                                                           |                                                                              |                                  |                  |

| Workspace: /home/user/LibrePCB-Work                                       | kspace                                                                       |                                  |                  |

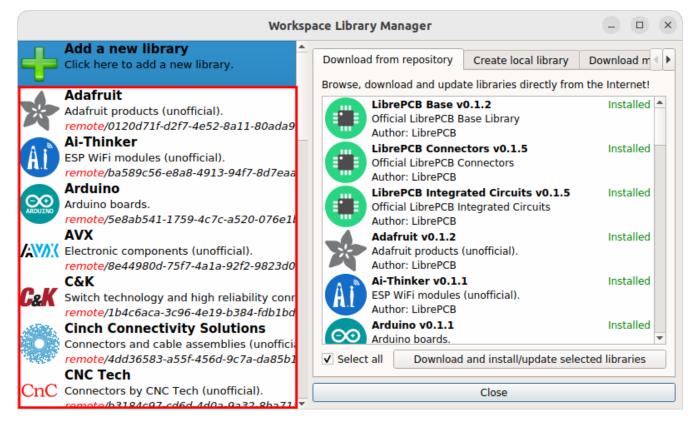

## **Install Remote Libraries**

Before you can start creating new projects, you need to add some libraries to your workspace. Libraries contain various kinds of elements which can be added to schematics and boards (e.g. symbols, footprints and devices).

Click on [ Library Manager ] in the control panel:

|                                                                           | Control Panel - Libr                                         | ePCB                         | – 🗆 x                              |

|---------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------|------------------------------------|

| <u>F</u> ile <u>E</u> xtras <u>H</u> elp                                  |                                                              |                              |                                    |

| This workspace does not contain<br>You should <u>open the library man</u> | any libraries, which are esse<br>ager to add some libraries. | ntial to create and modify p | rojects. <u>Don't show again</u> 🗙 |

| Workspace Projects                                                        | New Project                                                  | Open Project                 | Elibrary Manager                   |

|                                                                           | Recent Projects Project description                          | Favorite Projec              | ts                                 |

| Workspace: /home/user/LibrePCB-Work                                       | kspace                                                       |                              |                                    |

The library manager immediately fetches the list of available libraries from the Internet. Most of these libraries are hosted at github.com/LibrePCB-Libraries.

The most important library is *LibrePCB Base* because it contains commonly used library elements like resistors or diodes. It is highly recommended to install at least this library. However, you can even simply install all the available libraries at once:

| Workspace Library Manager                             |                                         |                           | - 🗆             | × |

|-------------------------------------------------------|-----------------------------------------|---------------------------|-----------------|---|

| Add a new library<br>Click here to add a new library. | Download from repository                | Create local library      | Download m      |   |

| •                                                     | Browse, download and upda               | te libraries directly fro | m the Internet! |   |

|                                                       | LibrePCB Base v                         | 0.1.2                     | Recommended     | • |

|                                                       | Official LibrePCB B<br>Author: LibrePCB | ase Library               | Install: 🗸      |   |

|                                                       | LibrePCB Conne                          | ctors v0.1.5              | Recommended     |   |

|                                                       | Official LibrePCB C<br>Author: LibrePCB | Connectors                | Install: 🗸      |   |

|                                                       | LibrePCB Integra                        | ated Circuits v0.1.5      | Recommended     |   |

|                                                       | Official LibrePCB I                     | ntegrated Circuits        | Install: 🗸      |   |

|                                                       | Author: LibrePCB                        |                           |                 |   |

|                                                       | Adafruit v0.1.2                         | ( (C ) ))                 |                 |   |

|                                                       | Adafruit products                       | (unofficial).             | Install: 🗸      |   |

|                                                       | Author: LibrerCB                        | 1                         |                 |   |

|                                                       | ESP WiFi modules                        | -                         | Install: 🗸      |   |

|                                                       | Author: LibrePCB                        |                           |                 |   |

|                                                       | Arduino v0.1.1                          | $\bigcirc$                |                 |   |

|                                                       | Arduino boards.                         |                           | Install: 🗸      | - |

|                                                       | ✓ Select all Download                   | and install/update sel    | ected libraries |   |

|                                                       |                                         | Close                     |                 |   |

Later you can keep the installed libraries up to date exactly the same way. Just open the library manager from time to time to see which libraries can be updated to a new version.

Dependencies between different libraries are automatically taken into account when changing the selection. So for example if you select *LibrePCB Connectors*, the *LibrePCB Base Library* will automatically be selected too because the connectors library depends on it.

Downloaded (so-called *remote-*) libraries are always read-only because otherwise local modifications could cause conflicts when updating the library the next time. But this is no problem, just follow this tutorial to create your own local library later. In a local library you can use or even override library elements from remote libraries by specifying a higher version number.

If you are familiar with version control systems (e.g. *Git*) and want to use them to manage your libraries (instead of the library manager), just clone the libraries into the subdirectory data/libraries/local/ in your workspace.

After the selected libraries have been downloaded, they will appear in the list of installed libraries on the left side of the library manager:

Note that after the libraries were installed, it takes a moment to create an index of all the contained elements. This process automatically runs in background and is indicated with a progress bar at the bottom right of all main windows. The installed libraries are ready to use once the progress bar disappears.

## **Create a Local Library**

In addition to the (read-only) remote libraries, you should create a personal, so-called *local* library. This is the place where you'll add your own symbols, footprints etc. later.

To do so, go to the *Create local library* tab, optionally enter some metadata (default values are good enough) and click on [ **Create Library**]:

|         | Workspa                                                                                                            | ace Library N         | Manager 2                             |                                                      | _ □           | × |

|---------|--------------------------------------------------------------------------------------------------------------------|-----------------------|---------------------------------------|------------------------------------------------------|---------------|---|

| +       | Add a new library<br>Click here to add a new library.                                                              |                       | om repository                         | Create local library                                 | Download m    | Þ |

|         | Adafruit<br>Adafruit products (unofficial).<br>remote/0120d71f-d2f7-4e52-8a11-80ada9<br>Ai-Thinker                 | Note: Please          | specify all attri<br>port for other l | ibutes in the english lang<br>anguages will be added | guage (locale |   |

| Aľ      | ESP WiFi modules (unofficial).<br>remote/ba589c56-e8a8-4913-94f7-8d7eaa<br>Arduino                                 | Name:<br>Description: | My Library                            |                                                      |               |   |

| ARDUINO | Arduino boards.<br>remote/5e8ab541-1759-4c7c-a520-076e1l<br>AVX                                                    | Author:<br>Version:   | Me<br>0.1                             | 3                                                    |               |   |

| /*///   | Electronic components (unofficial).<br>remote/8e44980d-75f7-4a1a-92f2-9823d0                                       | URL:                  |                                       | o the Git repository (opti                           |               | 5 |

| CeK     | C&K<br>Switch technology and high reliability conr<br>remote/1b4c6aca-3c96-4e19-b384-fdb1bd                        | License:              | CC0-1.0 (m<br>librepcb.org            | -                                                    | License       |   |

|         | Cinch Connectivity Solutions<br>Connectors and cable assemblies (unoff 4)<br>remote/4dd36583-a55f-456d-9c7a-da85b1 | Directory:            | My_Library.lpli                       | b<br>Create Library                                  |               |   |

| CnC     | CNC Tech                                                                                                           |                       |                                       | Close                                                |               |   |

If you're curious how the library looks like, select your library on the left and then click on [ **Open** Library Editor ] (or just double-click on your library):

|     | Work                                                                                                                       | space Library M                | lanager                         | _ | • × |

|-----|----------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|---|-----|

| -   | Add a new library<br>Click here to add a new library.                                                                      | <u> </u>                       |                                 |   |     |

|     | My Library<br>local/My_Library.lplib                                                                                       |                                |                                 |   |     |

|     | Adafruit                                                                                                                   | Name:                          | My Library                      |   |     |

| X   | Adafruit products (unofficial).<br>remote/0120d71f-d2f7-4e52-8a11-80ada9                                                   | Description:<br>Version:       | 0.1                             |   |     |

| Ai  | Ai-Thinker<br>ESP WiFi modules (unofficial).                                                                               | Author:<br>URL:                | Me                              |   |     |

|     | remote/ba589c56-e8a8-4913-94f7-8d7eaa<br>Arduino<br>Arduino boards.                                                        | Created:<br>Deprecated:        | Di. Okt. 18 17:09:00 2022<br>No |   |     |

|     | remote/5e8ab541-1759-4c7c-a520-076e1l<br>AVX                                                                               | Library Type:<br>Dependencies: | Local                           |   |     |

|     | Electronic components (unofficial).<br>remote/8e44980d-75f7-4a1a-92f2-9823d0                                               | Directory:                     | local/My_Library.lplib          |   |     |

| C-V | сак (2                                                                                                                     |                                | Open Library Editor             |   |     |

| UAN | Switch technology and high reliability com<br>remote/1b4c6aca-3c96-4e19-b384-fdb1bd                                        |                                | Remove this Library             |   |     |

|     | <b>Cinch Connectivity Solutions</b><br>Connectors and cable assemblies (unofficia<br>remote/4dd36583-a55f-456d-9c7a-da85b1 |                                | Close                           |   |     |

You'll see an empty library editor since the library doesn't contain any elements yet.

**Your workspace setup is now complete and ready to start creating your first PCB project!** You can close both the library editor and the library manager for now. We'll come back to the library editor later when we need to create our own library elements.

## **Create a PCB Project**

In LibrePCB, schematics and boards are always part of a project, so before creating schematics and boards you first need to create a project for every PCB. Click on **[ New Project ]** in the control panel:

|                                          | Control Panel - Libro | PCB               | - • ×           |

|------------------------------------------|-----------------------|-------------------|-----------------|

| <u>F</u> ile <u>E</u> xtras <u>H</u> elp |                       |                   |                 |

| Workspace Projects                       | New Project           | Open Project      | Library Manager |

|                                          | Recent Projects       | Favorite Projects |                 |

|                                          |                       |                   |                 |

|                                          | Project description   |                   |                 |

|                                          |                       |                   |                 |

| Workspace: /home/user/LibrePCB-Work      | kspace                |                   |                 |

Then specify some project metadata:

| Create New Project ×                                                    |                                                         |               |  |  |  |

|-------------------------------------------------------------------------|---------------------------------------------------------|---------------|--|--|--|

| Project Metadata<br>Specify some metadata of the project to be created. |                                                         |               |  |  |  |

|                                                                         | Name:<br>Author:<br>License:<br>Location:<br>Full Path: |               |  |  |  |

| 42091                                                                   |                                                         | Next > Cancel |  |  |  |

It's recommended to store projects within the workspace subdirectory named projects (the default location suggested by the wizard) because these projects are then shown in the control panel file explorer, making them easy to locate and use. But of course projects can be created at any other location as well.

$\bigcirc$

A LibrePCB project consists of a whole directory on the file system. While it is possible to manually add/modify files in that directory, generally you should avoid adding large files (e.g. datasheets) since this *could* slow down some operations. It's better to store unrelated files outside of the project directory.

Now you can choose whether the project should be initialized with a first schematic page and board, and how they are named. If you are unsure, just accept the default values:

|                                                                  | Create                      | New Project ×                        |  |  |

|------------------------------------------------------------------|-----------------------------|--------------------------------------|--|--|

| Initialization<br>Specify how the project should be initialized. |                             |                                      |  |  |

|                                                                  | ✓ Add B <u>o</u> a<br>Name: | Main<br>schematics/main/             |  |  |

|                                                                  |                             | < <u>B</u> ack <u>F</u> inish Cancel |  |  |

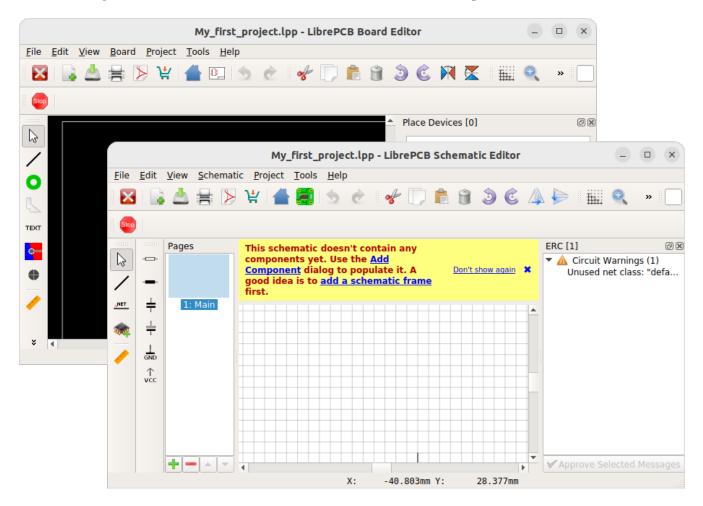

After clicking on [ Finish ], the schematic- and board editors show up:

### **Create Schematics**

Before starting with the board layout, a schematic will be needed. So let's see how to draw a schematic.

### Add Frame

First, you may want to add a frame to the schematic. Click on **[ Add Component ]** in the toolbar and select a schematic frame:

|                          | My_firs                                                                   | st_project.lpp - LibrePCB Schem | atic Editor 📃 💷 🗙                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|---------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>F</u> ile <u>E</u> di | it <u>V</u> iew <u>S</u> chematic <u>P</u> roject <u>T</u> o              | ols <u>H</u> elp                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | 3                                                                         | Add Component                   | × ×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                          | <ul> <li>Sensors, Transducers</li> <li>Single Board Computers,</li> </ul> | Schematic Frame                 | Schematic Frame     Variant:     4     5     Image: schematic frame     Image: schematic frame    < |

|                          |                                                                           | ✓ Ac                            | dd more                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                          | +                                                                         |                                 | Approve Selected Messages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                          |                                                                           | X: -41.642mm Y:                 | 22.836mm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

After clicking on **[OK]**, the selected component is attached to the cursor. Click on the origin of your schematics to place the frame at coordinate (0, 0).

Press Esc to finish the placement. The *Add Component* dialog pops up again to choose the next component. Press Esc again to leave the tool.

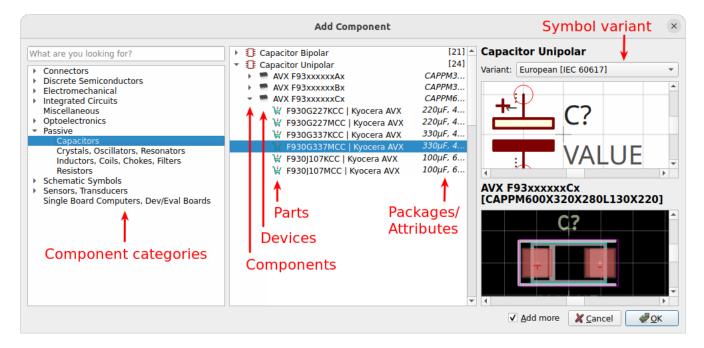

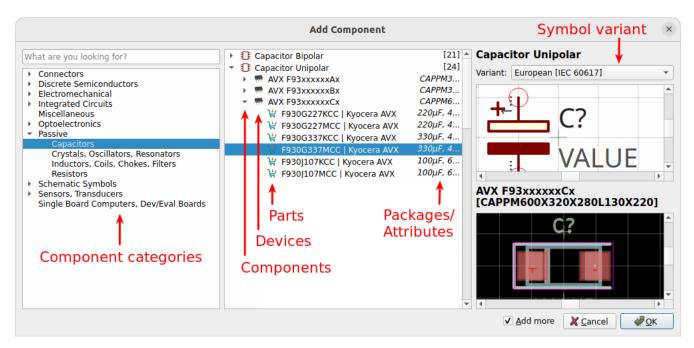

### Add Components/Devices

Now add all the resistors, capacitors, ICs etc. the same way to your schematic. However, for real parts (in contrast to the schematic frame) the dialog lets you select a concrete device. Here an explanation about the displayed information:

You can choose between adding a component a device or a part:

- **Component**: Defines the schematic symbol and netlist signals. It's all you need in a schematic, but it does not represent a concrete part and does not specify the package to be placed on the board.

- **Device**: Defines the package to be used in the board. Basically it's the combination of a component and a package with a particular pinout.

- **Part**: Represents a real, orderable part. In addition to defining the package, it also defines the exact MPN<sup>[1]</sup> which will appear in the BOM<sup>[2]</sup>.

To add something to a board, you need to choose a **device** or a **part**. However, it's your choice whether to select it *now* or *later* when starting with the board layout. This allows to draw the complete schematics even if various packages and devices do not exist yet in your libraries.

While placing components, press  $\mathbb{R}$  to rotate or  $\mathbb{M}$  to mirror. With Tab the focus is moved into the toolbar to allow specifying a value.

Supply symbols like VCC or GND are added exactly the same way since these are ordinary library elements as well. However, they are also provided in a dedicated toolbar for a quick access to the most commonly used elements.

The *Add Component* dialog lists all the components, devices and parts available in the libraries you have installed in your workspace. **If you are missing something, you either need to install more libraries or create your own library elements.**

E

To create your own library elements, follow the linked tutorial. You can keep the project open while working in the library editor. Afterwards, **wait for the background library scan to complete** (indicated as a progress bar at the bottom right of the window). Then the new library elements will appear in the *Add Component* dialog and are ready to be used.

#### **Draw Wires**

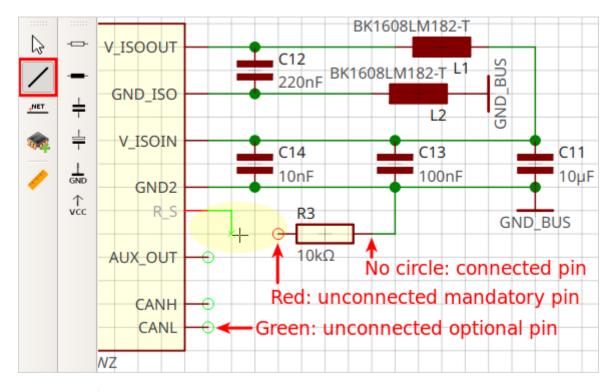

Once your schematic contains some components, the pins can be connected with the **[Draw Wire]** tool. Just click on a pin to start a new wire:

Pay attention to the circles around the pins. If a wire appears to be starting at a pin, but the circle is visible, it is **not** connected.

The color of the pin circles even provide some more context:

- **Red**: Mandatory pin, i.e. needs to be connected to a wire (if not, an ERC<sup>[3]</sup> warning is raised).

- **Green**: Optional pin, i.e. may or may not be connected, depending on the usecase. No ERC error will be raised if left unconnected.

#### Add Net Labels

To keep schematics clean and readable, net labels may be added. They allow to explicitly specify net names, and to create hidden connections between wires of the same net name.

- 1. Start the [ Add Net Label ] tool.

- 2. click on the wire where to attach the label.

- 3. Click to specify the label position.

While placing labels, press R to rotate.

|      | <br>ф    | x_001 | $ \bigcirc$ |             |      | 3G-5.08-H-GREEN |

|------|----------|-------|-------------|-------------|------|-----------------|

| 1    | -        | CANH  | CANH        | connections | CANH |                 |

| -NET | ÷        | CANH  | CANL        |             |      | - 3             |

|      |          | CANL  |             |             | CANL |                 |

|      | 1        |       |             |             |      |                 |

| -    | GND<br>1 |       |             | GND_BUS     |      | J2              |

All wires in the whole project which have the same name assigned will automatically be connected, even accross schematic pages.

### **Add More Sheets**

For larger projects, you may want to split the schematics into multiple sheets for better readability. Just add more sheets with **Schematic > New Sheet**, then add a frame and devices the same way. Use supply symbols and net labels to connect nets across pages.

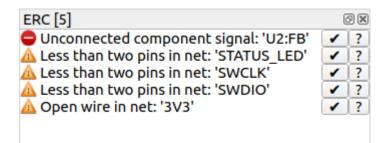

### **Electrical Rule Check**

At latest when you're finished with the schematics, you should check if there are no critical ERC messages. The ERC does not need to be triggered since it is automatically updated.

Open the ERC dock with **View > Go to Dock > Electrical Rule Check (ERC)**:

Click on [?] to get some more information about a message. If you're sure a message is not relevant, you could approve it with [ $\Box$ ] but usually warnings/errors should be fixed instead of approved.

### **Create Board**

Once the schematic is (more or less) complete, you can start designing the PCB in the board editor. If the board editor window is not opened already, click on the **[ Board Editor ]** toolbutton to open it.

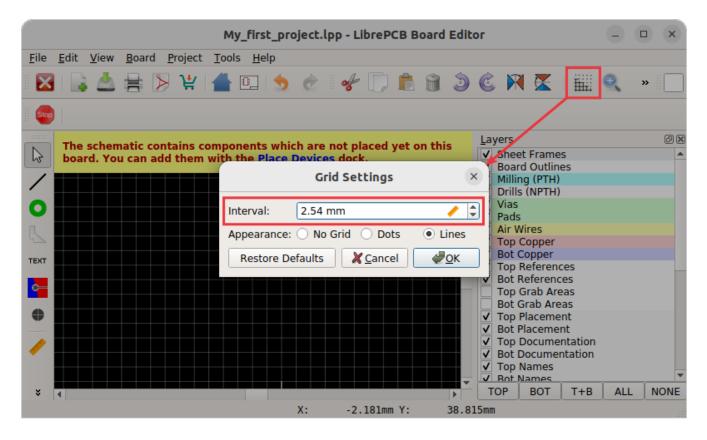

### **Set Grid Properties**

All board editor tools (e.g. the *Draw Trace* tool) work on a particular grid interval, i.e. the cursor snaps on a multiple of that value. The value might depend on the task you're working on so probably you'll need to change it several times while working on the board.

You can change it at any time with the **[ Grid Properties ]** toolbutton (or with F4):

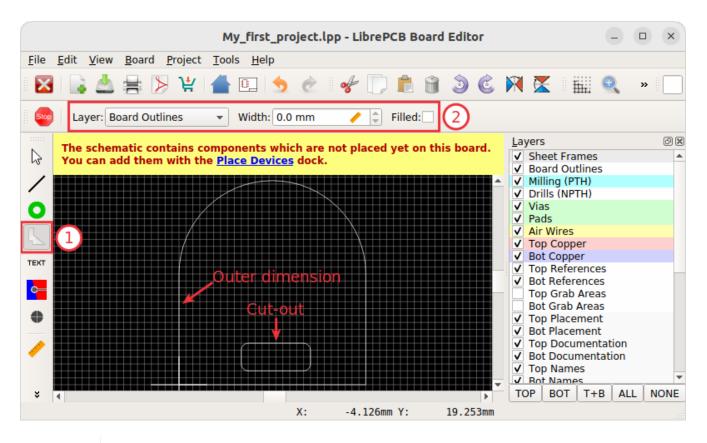

### **Draw Outlines**

The most important thing of the board is its outline. Generally there must be **a single**, **closed polygon on the** *Board Outlines* **layer**. It is recommended to set its **line width to 0.0mm** since — in contrast to many other polygons — this polygon does not represent any actual material but only the outer dimension of the PCB.

If your PCB needs non-plated cut-outs (e.g. slots, windows, ...), draw these polygons on the *Board Cutouts* layer with a width of 0.0mm.

A simple board outline polygon is automatically added by LibrePCB when creating a new project or board! So usually the only thing you need to do is to resize it to the desired size. The instructions here are intended only to explain more complicated scenarios and in case you want to re-draw the outline from scratch.

All polygons on the *Board Outlines* and *Board Cutouts* layers shall represent the actual board outlines (i.e. the edges), **NOT** the paths for the milling cutter! The PCB manufacturer will automatically offset the outline polygons to calculate the actual paths for the cutter.

Keep in mind that inner edges can only be produced with a specific minimum radius (corresponding to the milling cutter diameter of the PCB manufacturer). Although PCB manufacturers may produce your PCB anyway even if it contains inner edges with no or too small radius, it's highly recommended to draw all inner edges with a proper radius. Often a radius of 1.2mm or more works fine, while a smaller radius might lead to additional cost.

To draw polygons with arcs, open **[Properties]** from the polygon's context menu (right-click) and specify the vertex coordinates and angles manually.

A correct board outline is really crucial to avoid problems during the PCB manufacturing process! Make sure to fulfil these rules:

- There's exactly one polygon on the Board Outlines layer.

- Cut-out polygons (if there are any) are on the *Board Cutouts* layer and located fully inside the outer board outline.

- There are no tangent or intersecting polygons on these two layers.

- The line width of those polygons is 0.0mm (optional, but recommended).

- Polygons are closed (start and end coordinates are exactly identical) and consisting of a single polygon object (**NOT** multiple joined lines!).

- There are no other objects on these two layers.

$\bigcirc$

An easy way to check if the board outline is valid is to review the PCB in the 3D viewer. For that, open **View > Toggle 2D/3D Mode** or press Ctrl + 3.

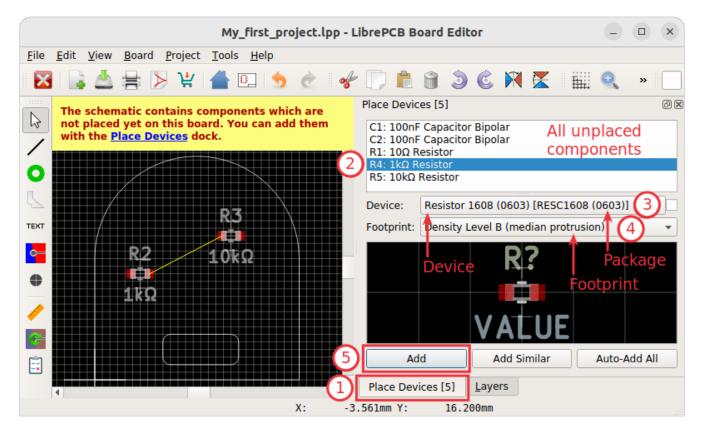

#### **Place Devices**

For every component in the schematic, you need to place a device in the board (except schematiconly components, like the schematic frame).

- 1. Open the *Place Devices* dock (View > Go to Dock > Place Devices).

- 2. Select a component to place.

- 3. Select the desired device for that component (not needed if the device is already specified in the schematics).

- 4. Choose the exact footprint to place, if there are multiple. Most packages have only one footprint if not, the default footprint is pre-selected.

- 5. Click **[ Add ]** and place the device with the cursor on the board. Press **R** to rotate or **F** to flip to the other board side while moving.

Repeat these steps until there are no more unplaced components.

$\mathbf{O}$

If you want to use the same device and footprint for all instances of a particular component, use the **[ Add Similar ]** button to add all at once.

If you can't find the desired device for a component (or the device dropdown is completely empty), you need to add the device to your local library first. Continue with the library element creation tutorial and come back to the board editor once the device is created.

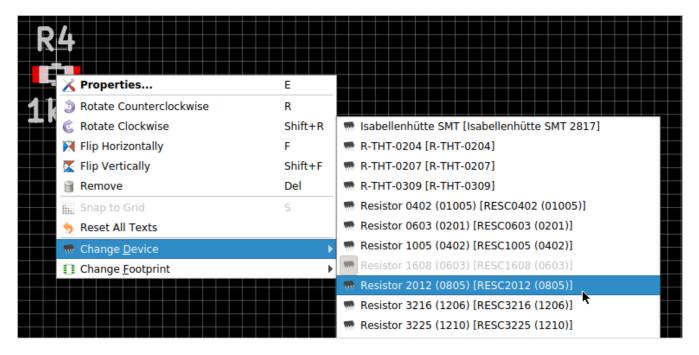

By the way, it's even possible to replace devices after adding them to the board. For example you can replace a 0603 resistor by a 0805 resistor using the **[ Change Device ]** context menu item (right-click):

Exactly the same way you can switch to a different footprint, just use the [Change Footprint] context menu item instead.

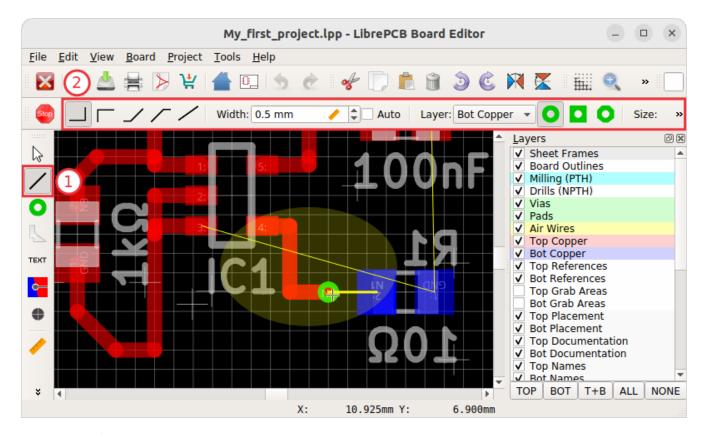

### **Draw Traces**

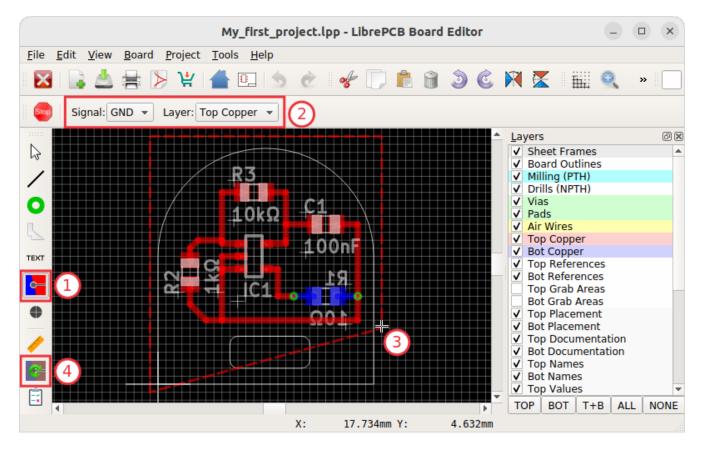

As soon as you add devices to the board, airwires will appear to show the missing traces. Start the **[Draw Trace]** tool and specify the trace settings in the toolbar. Then click on a pad to start a new trace:

The cursor automatically snaps on objects of the same net. If this is not desired, hold Shift while drawing.

With the right mouse button you can cycle through the different routing modes.

To switch to a different copper layer while drawing a trace, press Page Down (next lower layer) or Page Up (next higher layer). This will automatically insert a via if needed.

There are also shortcuts to change trace & via properties, see **Help > Keyboard Shortcuts Reference** for details.

#### **Add Planes (Copper Pours)**

If you need planes (also known as *copper pours*, i.e. filled copper areas to create electrical connections), proceed as follows:

- 1. Start the **[ Draw Plane ]** tool.

- 2. Specify the electrical net and copper layer in the toolbar.

- 3. Add vertices with mouse clicks. To fill the whole board, an approximate outline is good enough since it will be clipped automatically.

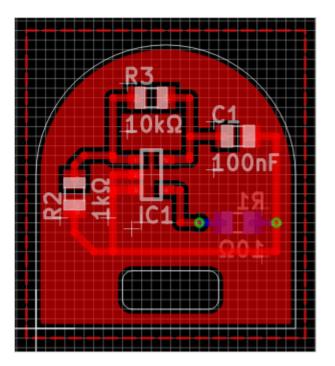

One the plane area is calculated, it appears with a filled area. As you can see, the area is automatically clipped to the board outline:

In case your plane does not get filled, make sure:

- The board outline polygon exists and fulfils all the rules listed above.

- The plane is located *within* the board outlines.

- There is at least one copper element of the same net located within the plane area e.g. a via, pad or trace. Plane areas which are not connected to any copper element are automatically discarded to avoid electrically "floating" copper areas on the board. If you prefer to add these copper areas anyway, open [Properties] from the plane context menu (right-click) and check the *Keep Islands* option.

To avoid plane areas cluttering up the view too much, they can be hidden with **View > Hide All Planes**. They will still be there, they are just hidden on the screen.

To interconnect planes on different copper layers, just place vias with the **[Add Via]** tool within the plane areas. Make sure the vias have the same net as the plane. Vias will also prevent plane fragments from disappearing if there's no other copper element within the plane and the *Keep Islands* option is disabled.

#### **Add Non-Plated Holes**

Non-plated holes can be added to the board with the **[ Add Hole ]** tool. Just specify the diameter and click on the desired position. Afterwards, use the **[ Properties ]** context menu item to specify the exact position if needed (e.g. if not located on the grid interval).

### **Design Rule Check**

Once your design is complete, you should run the design rule check (DRC) to ensure there are no critical mistakes.

But first you should check or adjust the design rules which are used to calculate via/pad restrings

and cream/stop mask clearances. For that, open **Board > Board Setup** or press **F7** and navigate to the **Design Rules** tab:

|                                                                                                      | В                | oard Se                 | etup              |          |                 |          | ×    |

|------------------------------------------------------------------------------------------------------|------------------|-------------------------|-------------------|----------|-----------------|----------|------|

| General Design Rules                                                                                 | DRC Settings     |                         |                   |          |                 |          |      |

|                                                                                                      | Minimur          | n                       | Ratio (% of Dia   | meter)   | Maximur         | n        |      |

| Stop Mask Clearance:                                                                                 | 0.1 mm           | / \$                    | 0.0%              | \$       | 0.1 mm          | /        | \$   |

| Solder Paste Clearance:                                                                              | 0.0 mm           | /                       | 10.0%             | \$       | 1.0 mm          | /        | \$   |

| Component Side Pads:                                                                                 | • Full Shape     | 🔾 Aut                   | omatic Annular I  | Ring     |                 |          |      |

| Inner Layer Pads:                                                                                    | O Full Shape     | <ul> <li>Aut</li> </ul> | omatic Annular I  | Ring     |                 |          |      |

| Autom. Pads Annular Ring:                                                                            | 0.25 mm          | / \$                    | 25.0%             | \$       | 2.0 mm          | /        | \$   |

| Vias Annular Ring:                                                                                   | 0.2 mm           | / \$                    | 25.0%             | \$       | 2.0 mm          | /        | \$   |

| Tented Vias Diameter:                                                                                |                  |                         |                   |          | 0.5 mm          | /        | \$   |

| Note: These settings define<br>stop masks, where not mar<br>(DRC) at all. In contrast to t<br>board. | nually overridde | en). The                | y are not related | l to the | design rule che | eck      | e.g. |

|                                                                                                      |                  |                         | 🖌 Apply           | X        | Cancel          | <u> </u> | <    |

Actually it's better to set the design rules *before* drawing traces and adding planes since they affect the clearances. It is only moved to the end of the boards tutorial to keep the focus on the design workflow.

Fortunately, usually the default values are fine. So if you're unsure about these values, just keep the defaults.

Afterwards, navigate to the next tab called **DRC Settings** and configure the settings according the capabilities of your desired PCB manufacturer:

i

|                        |                   | Bo  | ard | l Setup                                |                     | ×  |

|------------------------|-------------------|-----|-----|----------------------------------------|---------------------|----|

| General Design Rul     | es DRC Settings   |     |     |                                        |                     |    |

| Clearances             |                   |     |     |                                        |                     | -  |

| Copper ↔ Copper:       | 0.2 mm            | /   | -   | Copper ↔ Board Edge:                   | 0.3 mm 🥒            | \$ |

| Copper ↔ Holes:        | 0.25 mm           | 1   | -   | Silkscreen $\leftrightarrow$ Stopmask: | 0.127 mm 🥒          | \$ |

| Drill ↔ Drill:         | 0.35 mm           | /   | *   | Drill ↔ Board Edge:                    | 0.5 mm 🧳            | \$ |

| Minimum Sizes          |                   |     |     |                                        |                     | -  |

| Copper Width:          | 0.2 mm            | /   | *   | PTH Annular Ring:                      | 0.2 mm 🧳            | \$ |

| NPTH Drill Diameter:   | 0.3 mm            | /   | -   | NPTH Slot Width:                       | 1.0 mm 🥒            | \$ |

| PTH Drill Diameter:    | 0.3 mm            | /   | -   | PTH Slot Width:                        | 0.7 mm 🥒            | \$ |

| Silkscreen Width:      | 0.15 mm           | /   | -   | SIlkscreen Text Height:                | 0.8 mm 🥒            | \$ |

| Outline Tool Diameter: | 2.0 mm            | /   | -   |                                        |                     |    |

| Allowed Features       |                   |     |     |                                        |                     | -  |

| Via Types:             | Blind Vias        |     |     | Buried Vias                            |                     |    |

| NPTH Slots:            | Only Simple Oblor | ngs | Ŧ   | PTH Slots:                             | Only Simple Oblongs | •  |

|                        |                   |     |     | ✓ Apply                                | X Cancel            |    |

If you're unsure, just skip this for now (the default values are usually fine).

Once all settings are configured, open **Board > Design Rule Check** or press F8 to run the DRC. This can take some time. The DRC dock widget should automatically appear to display the result:

| My_first_pro                                   | oject.lpp - L | LibrePCB Board Editor – 💷 🗙                                                                                                                                |

|------------------------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>File Edit View Board Project Tools Help</u> |               |                                                                                                                                                            |

| 🔀 📄 📥 🚔 🔊 🐉 🦊 📥 💽                              | 5 è           | 🛷 💭 🛍 🗃 🌢 🕲 🏹 🔀 🏭 » 🗈                                                                                                                                      |

| Stop                                           |               |                                                                                                                                                            |

|                                                | -             | DRC [8]                                                                                                                                                    |

| 8                                              |               | Clearance plane ↔ board outline < 0.3 mm ✓ 1<br>Clearance trace ↔ board outline < 0.3 mm ✓ 1                                                               |

|                                                |               | Clearance trace ↔ board outline < 0.3 mm                                                                                                                   |

|                                                |               | A Board outline inner radius < 1.0 mm                                                                                                                      |

|                                                |               | △ Clearance silkscreen text $\leftrightarrow$ stop mask < 0.127 mm<br>✓ T<br>△ Clearance silkscreen text $\leftrightarrow$ stop mask < 0.127 mm<br>✓ T     |

|                                                |               | $\triangle$ Clearance silkscreen text ↔ stop mask < 0.127 mm $\checkmark$ 3<br>$\triangle$ Clearance silkscreen text ↔ stop mask < 0.127 mm $\checkmark$ 3 |

|                                                |               | Clearance silkscreen text ↔ stop mask < 0.127 mm                                                                                                           |

|                                                |               |                                                                                                                                                            |

|                                                | $\setminus$   | Open DRC settings 🔪                                                                                                                                        |

|                                                |               |                                                                                                                                                            |

|                                                |               | Run DRC                                                                                                                                                    |

|                                                |               | Run quick check 🔨                                                                                                                                          |

| <b>100n</b>                                    |               |                                                                                                                                                            |

|                                                |               | ✓ Zoom to location                                                                                                                                         |

| × 4                                            | × ·           | Place Devices [0] Layers ERC [0] DRC [8]                                                                                                                   |

|                                                | X: 9          | .421mm Y: 13.012mm                                                                                                                                         |

Then just click on a message to highlight the issue in the board editor. Or click on [?] to get some more information about a message. If you're sure a message is not relevant, you could approve it with [ ] but usually warnings/errors should be fixed instead of approved.

There's also a tool named **Quick Check** which runs only the most important checks of the DRC. It is intended to be run regularly while working on the layout and can be triggered with Shift + F8.

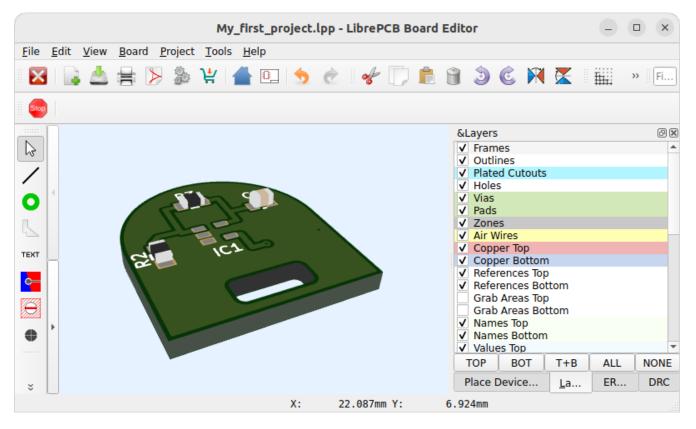

#### **3D Preview**

Once you fixed all ERC issues, it's highly recommended to review the PCB in the 3D viewer. If anything with the board outline, the device placement or something like that is not correct, chances are high you will notice that in the 3D view. Click on **View > Toggle 2D/3D Mode** or press Ctrl + 3 to open it (press it two times for fullscreen):

Note that not all packages have a 3D model assigned, like the OpAmp in our example. But no worries, this does not cause any issues.

If everything looks as expected, you're ready to order the PCB!

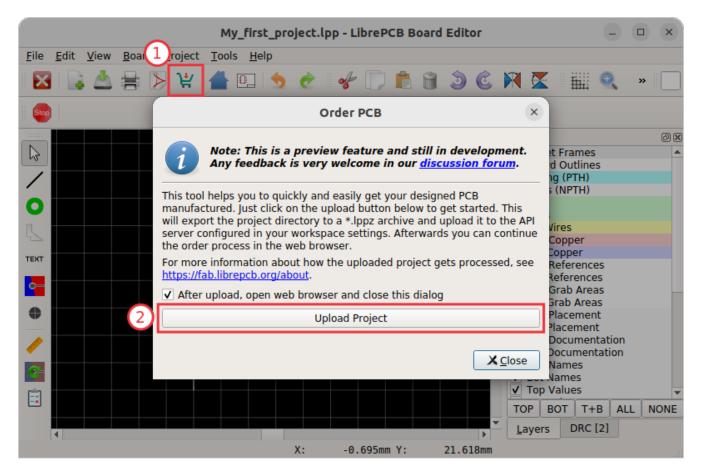

### **Order PCB**

The easiest and fastest way to order the PCB is LibrePCB Fab. It automatically exports and uploads all the necessary production data files without annoying you with the whole traditional production data workflow. See fab.librepcb.org/about for more information.

You prefer to manually generate the production data files? Or you want to use a PCB manufacturer not available at LibrePCB Fab? No problem! Just skip this

### LibrePCB Fab

To start the order process, click the [Order PCB] toolbutton in either the schematic- or board editor:

With **[Upload Project]**, the project is uploaded to our order service **fab.librepcb.org**. Then your web browser should open a website where you can review and continue the order.

Alternatively you could also export your LibrePCB project as a \*.lppz archive (File > Export > Export \*.lppz Archive) and then upload this file with the web browser on fab.librepcb.org. This procedure might be useful if for some reason the direct upload is not desired or doesn't work (e.g. due to a corporate firewall).

#### **Generate Production Data**

Instead of using LibrePCB Fab, of course you can also generate the production data manually and forward these files to any PCB manufacturer you like.

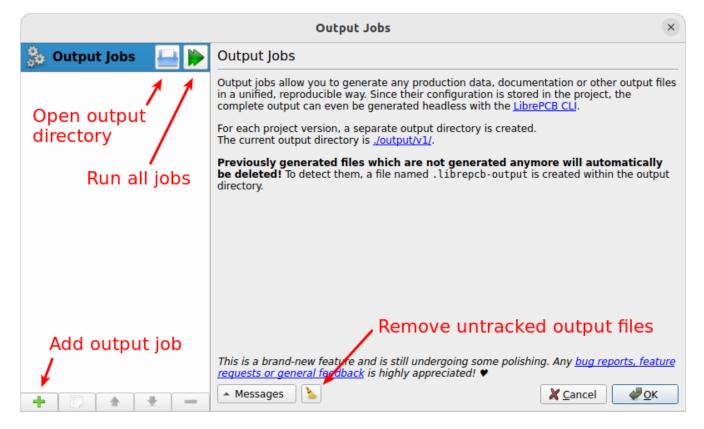

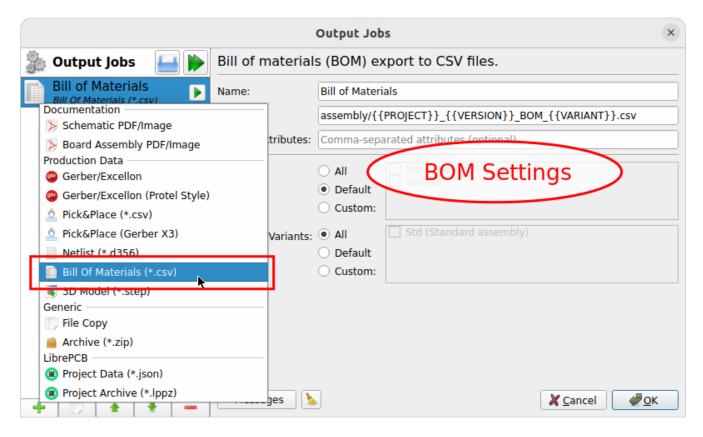

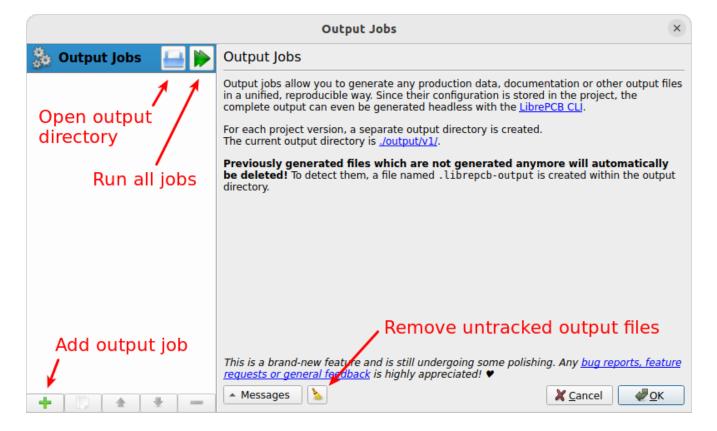

Currently there exist multiple ways how to generate production data, but it's recommended to use the **Output Jobs** feature for that. Click on **File > Output Jobs** or press **F11** to open the corresponding window:

Then for any output you like to generate, click on the [+] button at the bottom left. See the following sections for details on the available jobs.

Any files generated through output jobs will be written to the path ./output/<VERSION>/ within the project directory, where <VERSION> is the project's version number as defined in the **Project Setup** dialog. So make sure the version number is set as desired to avoid overwriting e.g. the output files of a previous PCB version.

Once you set up all output jobs, just click on the "Run all jobs" button and all files will be written to the output directory. Then click on **[OK]** and save the project to store the output jobs configuration.

#### Gerber/Excellon

For the Gerber/Excellon production data you need to choose the settings of the Gerber/Excellon export. There are two different presets built-in, a default style and a Protel style. Generally you should determine what format your PCB manufacturer accepts. Many manufacturers accept Protel-style settings, so if you're unsure, choose **Gerber/Excellon (Protel Style)**.

|      |                                                                                             |                    | Output Jobs                    |                                    |                            | × |  |  |  |  |

|------|---------------------------------------------------------------------------------------------|--------------------|--------------------------------|------------------------------------|----------------------------|---|--|--|--|--|

| Sec. | <b>Output Jobs</b> Gerber (RS-274X) / Excellon (XNC) PCB production data export for boards. |                    |                                |                                    |                            |   |  |  |  |  |

| gþr  | Gerber/Excellon<br>Gerber/Excellon                                                          |                    |                                |                                    |                            |   |  |  |  |  |

|      | Documentation                                                                               | simpler and fast   | ter alternative, you could use | the <u>Order PCB</u> feature inste | ad.                        |   |  |  |  |  |

|      | Schematic PDF/Image Board Assembly PDF/Image                                                | e:                 | Gerber/Excellon                |                                    |                            |   |  |  |  |  |

|      | Production Data                                                                             | Path:              | gerber/{{PROJECT}}_{{VERSION}} |                                    |                            |   |  |  |  |  |

|      | <ul> <li>Gerber/Excellon</li> <li>Gerber/Excellon (Protel Style)</li> </ul>                 | nes:               | _OUTLINES.gbr                  | Inner Copper:                      | _COPPER-IN{{CU_LAYER}}.gbr | 9 |  |  |  |  |

|      | Gerber/Excellon (Proter Style)     Pick&Place (*.csv)                                       | opper:             | _COPPER-TOP.gbr                | Bottom Copper:                     | COPPER-BOTTOM.gbr          |   |  |  |  |  |

|      | 🛕 Pick&Place (Gerber X3)                                                                    | topmask:           | Soldermask                     | er/Excellon Setti                  | ngs ERMASK-BOTTOM.gbr      | ] |  |  |  |  |

|      | Netlist (*.d356)                                                                            | ilkscreen:         | _SILKSCREEN-TOP.go             | Bottom Silkscreen:                 | _SILKSCREEN-BOTTOM.gbr     |   |  |  |  |  |

|      | Bill Of Materials (*.csv)                                                                   | NPTH:              | _DRILLS-NPTH.drl               | Drills PTH:                        | _DRILLS-PTH.drl            |   |  |  |  |  |

|      | Generic                                                                                     | erge PTH and N     | PTH drills into one file:      |                                    | _DRILLS.drl                | - |  |  |  |  |

|      | 📄 File Copy                                                                                 | Blind/Buried:      | _DRILLS-PLATED-{{START_L       | _AYER}}-{{END_LAYER}}.dr           | 1                          |   |  |  |  |  |

|      | Archive (*.zip) LibrePCB                                                                    | se drilled slot co | mmand in Excellon files (G85   | 5)                                 |                            |   |  |  |  |  |

|      | 🛞 Project Data (*.json)                                                                     | on Solder Paste    |                                | - Bottom Solder Past               | e (,                       |   |  |  |  |  |

| -    | Project Archive (*.lppz)                                                                    | lessages 💧 🍆       |                                |                                    | 🗶 <u>C</u> ancel 🖉 🖉 OK    |   |  |  |  |  |

If required, the settings can now be adjusted manually.

It's highly recommended to cross-check the generated files with third-party tools like gerbv or the reference Gerber viewer. LibrePCB developers are not responsible for any implications caused by wrong production data.

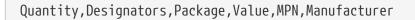

#### Pick&Place Data

If you also need pick&place files for automated assembly, just choose **Pick&Place (\*.csv)** (or alternatively ther Gerber X3 variant):

|                                                                                                                                                                                                                          |         | Ou                                  | itput Jobs                                                                 |            |               |                                        | ×            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------------------|----------------------------------------------------------------------------|------------|---------------|----------------------------------------|--------------|

| 🐁 Output Jobs 🛛 📔 ┣                                                                                                                                                                                                      | CSV pic | k&place p                           | osition fil                                                                | e export f | or boards.    |                                        |              |

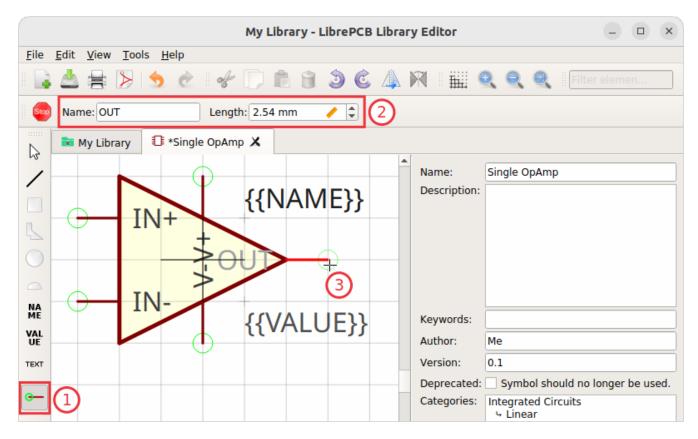

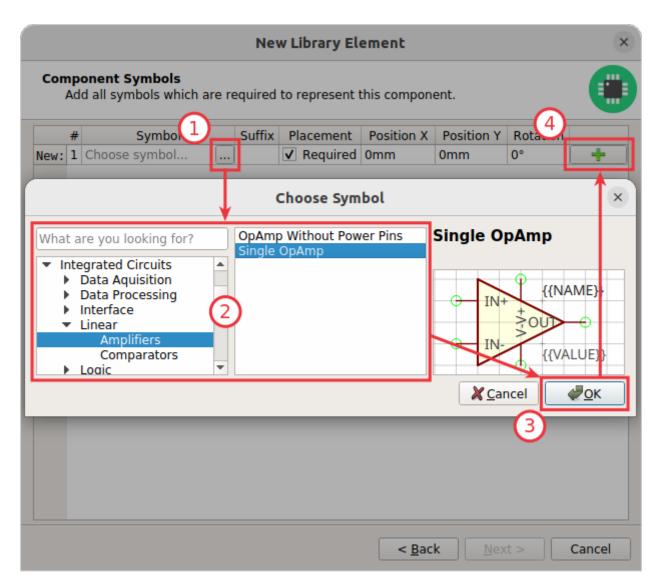

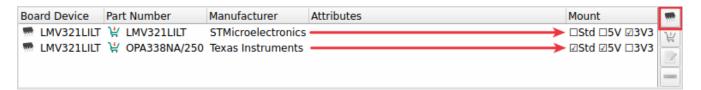

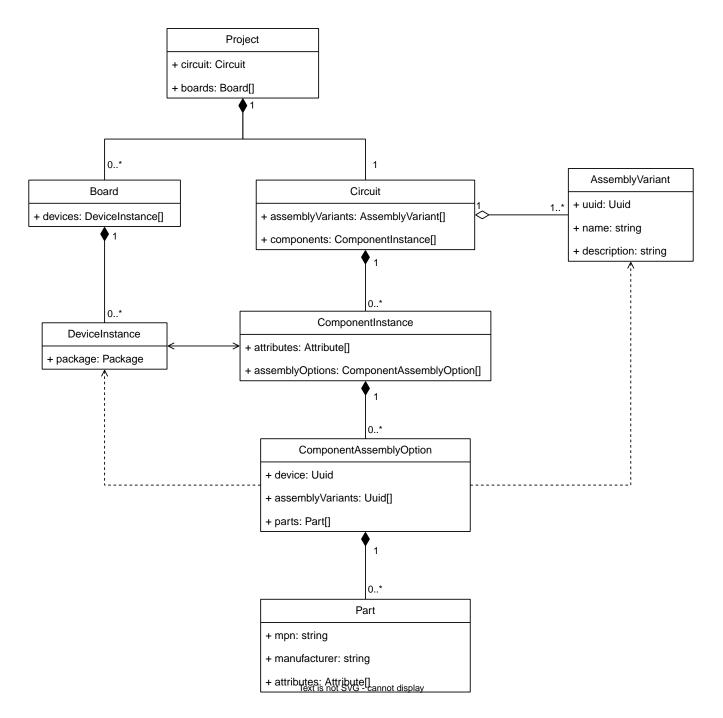

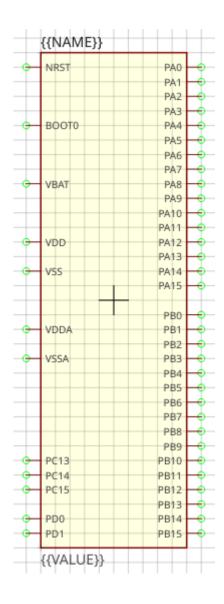

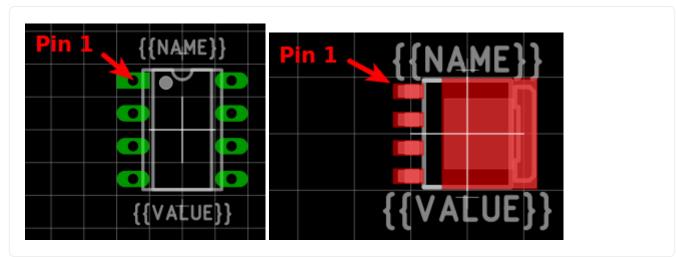

| Pick&Place CSV                                                                                                                                                                                                           | Name:   |                                     | Pick&Place                                                                 | CSV        |               |                                        |              |